RISC-V and the Future of DPUs

As the DPU market surges, RISC-V offers a customizable, open alternative to ARM’s dominance — potentially redefining datacenter infrastructure.

9/2/20253 min read

Can RISC-V Redefine the DPU Race?

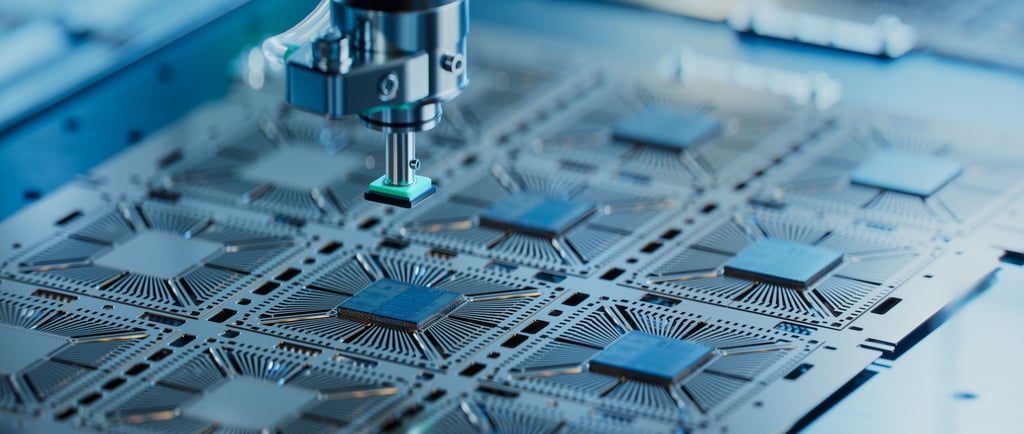

For years, the datacenter conversation has revolved around CPUs and GPUs. Intel and AMD fought for x86 supremacy, NVIDIA reshaped high-performance computing with GPUs, and ARM steadily expanded its presence. But beneath this high-profile competition, another quiet revolution has been unfolding — the rise of the Data Processing Unit (DPU).

The Silent Coup: How ARM Captured DPUs

DPUs, also known as SmartNICs, are specialized processors that handle the “plumbing” of the datacenter. They offload essential tasks such as:

Packet processing, TCP/IP, and RDMA

Storage services like compression, encryption, and NVMe-over-Fabrics (NVMe-oF)

Security isolation in multi-tenant cloud environments

Orchestration and workload management that free up CPU resources

When the opportunity emerged, ARM stepped in quickly. Its small, power-efficient cores were already well integrated into networking silicon, making them a natural fit for DPUs. As a result, companies such as NVIDIA (BlueField), Marvell (OCTEON), AMD (Pensando), and Broadcom all standardized on ARM. By the time Intel responded with its Infrastructure Processing Unit (IPU) initiative, ARM had already built the ecosystem and set the standard.

A Market on the Rise

The global Data Processing Unit (DPU) market is projected to grow from $1.5 billion in 2023 to approximately $9.8 billion by 2032, representing a 22.8% CAGR (Dataintelo Consulting Pvt. Ltd., 2024).

The drivers behind this growth are clear: explosive data generation, rising demand for efficient data processing, and the need for secure, isolated workloads in multi-cloud environments. Currently, ARM-based DPUs dominate shipments, but the market’s expansion has created an opening for new players.

RISC-V Enters the Scene

RISC-V brings a fundamentally different approach to DPUs. As an open instruction set architecture (ISA), it allows companies to customize processors for their specific workloads, avoiding the licensing restrictions and royalties associated with ARM.

This flexibility is particularly relevant for DPUs, which integrate multiple roles:

Scalar compute for control-plane tasks

Vector compute for packet processing, cryptography, and storage acceleration

Matrix compute for AI inference, telemetry, and advanced analytics

Over the past decade, RISC-V has evolved from simple scalar cores to include robust vector and now matrix extensions, creating an ISA that maps naturally onto the diverse requirements of DPUs.

Companies Driving RISC-V DPUs

Several companies are advancing RISC-V into datacenter-class workloads:

SiFive: Linux-capable cores with early vector adoption and strong ecosystem support

Andes Technology: Embedded processors extended with DSP and vector instructions

Akeana: Datacenter CPUs with simultaneous multithreading (up to four threads) and matrix engines

Ventana Micro Systems: Server-class RISC-V CPUs aligned with hyperscaler requirements

SemiDynamics: Configurable HPC cores optimized for memory-intensive vector workloads

Simplex Micro: Unified scalar/vector/matrix execution pipelines for deterministic performance

XiangShan: Open-source research exploring unified architectures

These efforts reflect how RISC-V can evolve beyond edge devices and CPUs to become a central player in datacenter infrastructure.

Leapfrogging ARM or Coexisting?

The critical question is whether RISC-V will replace ARM in DPUs or simply coexist alongside it.

ARM’s strength lies in incumbency and proven deployments across major vendors.

RISC-V’s opportunity comes from its open, customizable model that blends scalar, vector, and matrix programmability into a single platform.

For hyperscalers and infrastructure vendors, this represents a chance to avoid vendor lock-in, optimize for power and performance, and maintain greater architectural sovereignty.

Why This Shift Matters

The emergence of RISC-V in DPUs is more than a new entrant challenging an incumbent. It represents a chance to redefine the category itself. Instead of being locked into fixed-function accelerators and scalar cores, DPUs can evolve into fully programmable platforms — orchestrating networking, storage, and AI flows simultaneously.

In this scenario, DPUs stop being mere offload engines and instead become programmable infrastructure processors that reshape datacenter efficiency.

Conclusion

The industry has long viewed RISC-V as either a CPU challenger or an IoT enabler. Yet the real disruptive opportunity may lie in the control plane of the datacenter. ARM built its DPU leadership by capturing a market Intel and AMD overlooked. Today, RISC-V has the chance to open the next chapter — offering customization, sovereignty, and a roadmap aligned with the needs of modern workloads.

The result may not be a direct battle for replacement but rather coexistence, with ARM maintaining incumbency and RISC-V offering an open alternative. What is clear is that as datacenters grow more AI-driven and complex, the DPU will become central to infrastructure strategy — and RISC-V could redefine its future.

Source - Semiwiki

QUICK LINKS

NEIL RAO TOWERS, 117 & 118, Rd Number 3, Vijayanagar, EPIP Zone, Whitefield, Bengaluru, Karnataka 560066

200/2, Tada Kandriga, Tada Mandalam, Tirupati District - 524401

Locations